1 Introduction

USB (Universal Serial Bus) has been widely used for its configuration, plug-and-play and other features. The USB 2.0 standard proposed in 2004 has a transmission speed of up to 480 Mbps. However, in the USB 3.0 standard, its maximum transmission speed is almost 10 times that of the conventional USB 2.0 transmission rate, reaching 5.0 Gbps, which is defined as " Super high speed USB interface". This article is based on CYPRESS's FX3 series USB3.0 chip, research and development of USB3.0 bus.

2.USB3.0 interface chip overview

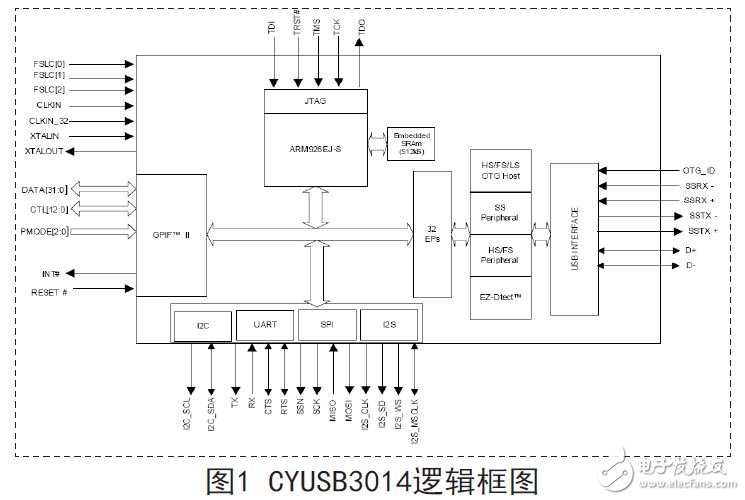

Cypress's EZ-USB FX3 is a next-generation USB 3.0 peripheral controller with highly integrated and flexible features that allows system designers to add USB 3.0 to any system. This article uses the FX3 series USB3.0 chip CYUSB3014.

The FX3 is fully compatible with the USB 3.0 V1.0 and USB 2.0 specifications. The integrated USB 2.0 OTG controller allows the chip to be used as a master and slave device. In addition, it supports some common peripheral interfaces such as SPI, I2C, UART and I2S to communicate with external devices.

The FX3 features a fully configurable parallel general-purpose programmable interface, GPIF II, that can interface with any processor, ASIC or FPGA. It can be easily and seamlessly connected to a variety of common interfaces, such as asynchronous SRAM, asynchronous and synchronous address data multiplexed interfaces, parallel ATA, and more. EZ-USB FX3 integrates USB3.0 and USB2.0 physical layer (PHY) and 32-bit ARM926EJ-S microprocessor with powerful data processing capabilities and can be used to build custom applications.

3. System overall design

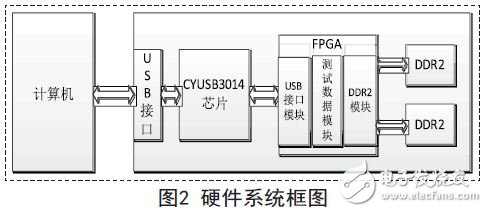

The system design is mainly composed of software part and hardware part. The software part mainly includes three parts: PC application, FX3 firmware, and FPGA program. The hardware part is mainly composed of FPGA, USB3.0 chip and DDR2. The system block diagram of the hardware is shown in Figure 2. This paper mainly completed the design of hardware, PC application and FPGA program.

The FX3 firmware program uses the firmware of the Cypress SDK development kit.

3.1 DDR module design

Compared to FPGA, USB3.0 interface is a high-speed receiving unit. Data caching is an indispensable part between systems with different working speeds. In general, the use of FIFO can basically make each system work at its own clock frequency without the need for repeated handshake signals. communicate with. The data designed in this paper is stored on the computer. Since the hardware configuration of each computer may be different, we designed the DDR2 virtual FIFO module for data caching, which can provide enough cache for batch transfer, without worrying that the cache is not enough for the computer. Accessing data causes data loss.

This system selects two MT47H64M16HR, two DDR parallel control bus and address bus, the total storage capacity reaches 2Gbit, the read and write width is 16bit, it has abundant resources, enough to meet the needs of this system.

3.2 USB3.0 interface design

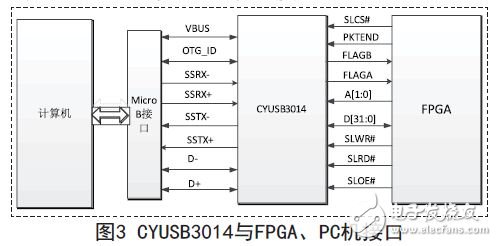

Unlike USB 2.0, USB3.0 has its own dedicated data path, dedicated data transmission line and independent data receiving line when communicating with the computer, namely the four-wire differential signals SSRX+/- and SSTX+ in Figure 3. /-, so you can really achieve full duplex. At the same time, USB3.0 is also compatible with the USB2.0 D+/- signal interface, so that it can be seamlessly connected to USB2.0. Using the slave FIFO interface to link to the FPGA, the transfer speed can reach 320MBps. Figure 3 shows the circuit connection between the USB chip and the FPGA and PC.

3.3 FPGA logic design

The FPGA is the core of the whole system. It needs to generate test data and store the data in DDR2, and transfer the data read out in DDR2 to the internal FIFO of CYUSB3014. Therefore, it is mainly composed of the module shown in Figure 2.

The Mechanical Buzzer uses a magnet to move a reed up and down quickly to emit a lower-pitch buzz! It's quieter than the Piezoelectric Buzzer but uses more power, so you the terminals will have to be closer to the battery packs. To use them, you'll need to match the wire colors to the wires from the battery pack.

Mechanical Buzzer

Piezo Beeper,Mechanical Buzzer,Piezo Mechanical Buzzer,Low Frequency Mechanical Buzzer

Jiangsu Huawha Electronices Co.,Ltd , https://www.hnbuzzer.com